Simon Alexander Oelgeschläger

# SRAM / DRAM

Eine Präsentation im Modul Proseminar Speicher- und Dateisysteme

## Präsentationsstruktur

- Datenspeicher

- DRAM

- SRAM

- Zusammenfassung / Vergleich

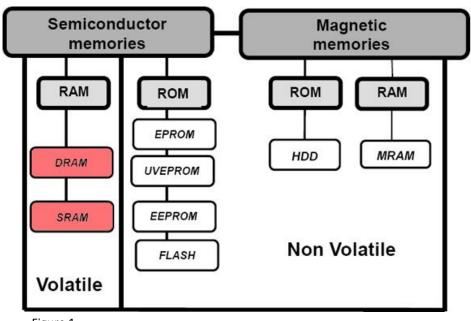

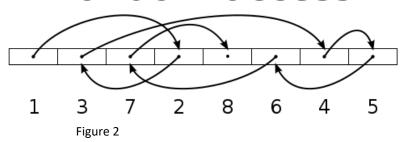

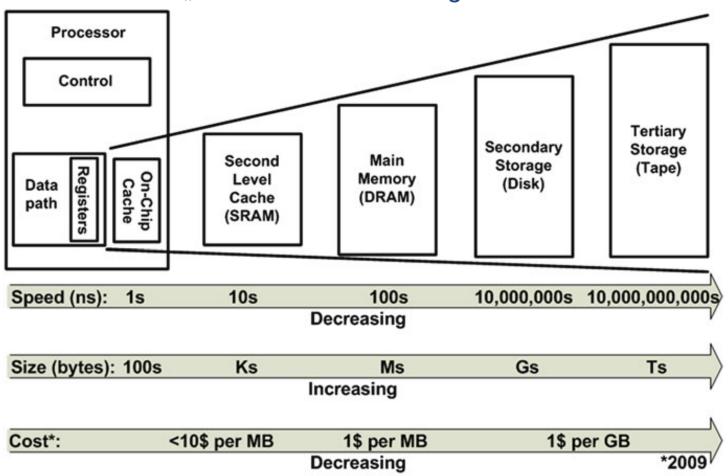

## **Speichermedien**

Jegliche Art von Medien, die jegliche Art von Daten speichert (Computer)

Datenspeicher für elektronische Geräte:

- Elektronische Speicherung Halbleiterspeicher

- andere Datenträger Festplatten – magnetisch DVDs optisch

Figure 1

## Flüchtiger und nichtflüchtiger Speicher

volatile memory (flüchtig)

non-volatile memory (nichtflüchtig)

- Daten bleiben nur bei konstanter Stromversorgung erhalten

- Kurze Zugriffszeit

- Höherer Preis pro Speichereinheit

zB. SRAM / DRAM

- Speicherung von Daten auch ohne anliegende Spannung

- Längere Zugriffszeit

- Niedriger Preis pro Speichereinheit

zB. HDD Festplatten, SSDs

- Halbleiterkristall mit mikroelektrischen Speicherstrukturen

- 1-Bit-Speicherelement mit wenigen Kondensatoren und Transistoren (zB. MOSFETs)

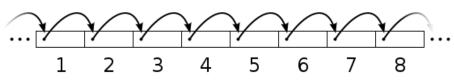

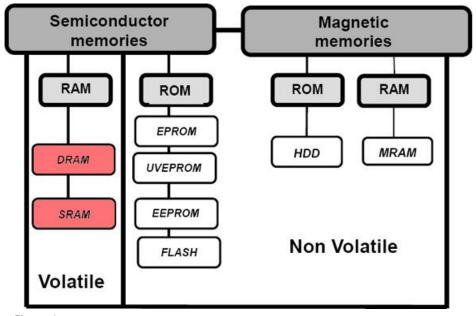

#### Sequentieller Zugriff:

zB. Kassette Schriftrolle

Wahlfreier Zugriff:

Random-Access Memory (RAM)

## Sequential access

## Random access

#### SRAM / DRAM

#### Halbleiterspeicher

- Eher hoher Preis pro Speichereinheit

- Niedrige Zugriffszeit

#### Speicher mit wahlfreiem Zugriff (RAM)

- Niedrige Zugriffszeit

- Effizientes Lesen und Schreiben

#### Flüchtiger Speicher

- Niedrige Zugriffszeit

- Eher hoher Preis pro Speichereinheit

Fokus: Schnell Lesen und Schreiben

Figure 1

- Übersicht

- Aufbau

- Funktionsweise

- Probleme & Lösungen

- Entwicklung / Potenzial

- Einsatzgebiet

- Produktion / Markt

Figure 3

### "Übersicht"

Eine Art von Random-Access Memory, welche jedes Datenbit in einem kleinen Kondensator innerhalb eines integrierten Schaltkreises speichert.

- Flüchtiger Speicher

- Dynamic-RAM

- Symmetrische Lese- und Schreibgeschwindigkeit

- Sehr lange Lebensdauer der Zellen (non-destructive read & write)

- Gutes Preis- / Leistungsverhältnis, gute Verfügbarkeit

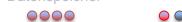

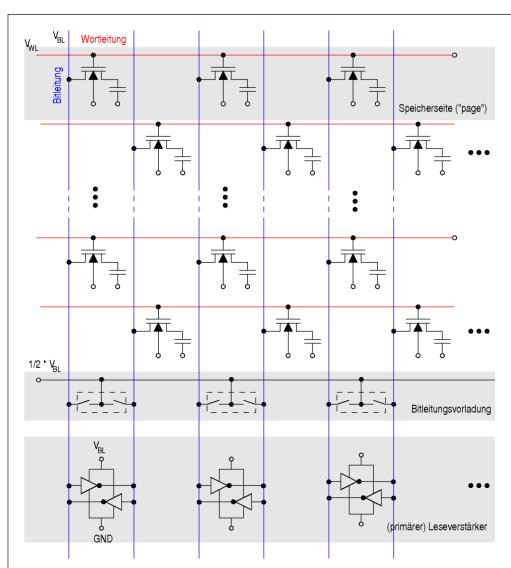

#### "Aufbau"

Speicherzelle mit 1 Bit Speicherkapazität bestehend aus einem Kondensator sowie einem Transistor

- Ansteuerung über eine Wortleitung sowie eine Bitleitung

- Auslesen des Datenbits durch minimale Spannungsunterschiede im System

- Limitierende Faktoren

Figure 4

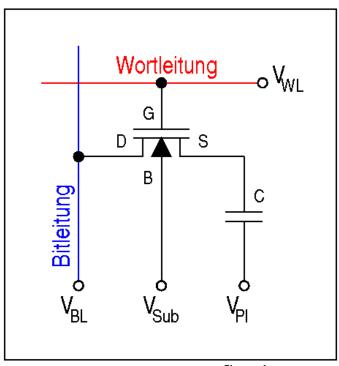

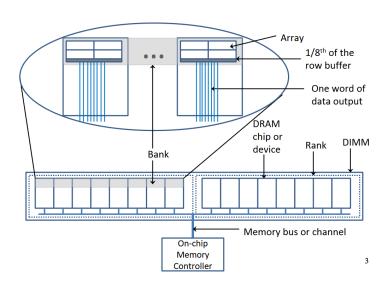

## "Aufbau"

Figure 5 Figure 6

#### "Funktionsweise"

- Ansteuerung einer Zeile über Adresse der jeweiligen Wortleitung

- Auslesen des Zustands / Werts der einzelnen Zelle über die korrespondierende Bitleitung

- Verstärkung und Weiterleitung durch den Leseverstärker sowie den row-buffer

Figure 7

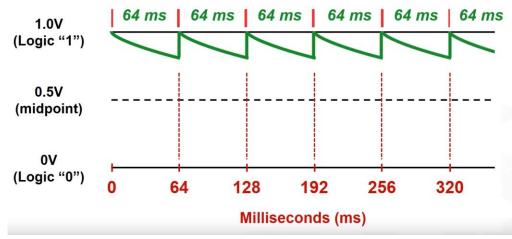

#### "Funktionsweise"

- Dauer einer Leseanforderung ist gleich der einer Schreibanforderung, aber:

- Jeder Lesezyklus muss von einem Schreibzyklus gefolgt sein

- Refresh wird normalerweise vom Modul selber gesteuert

Figure 8

#### "Probleme & Lösungen"

Geringe Geschwindigkeit (durch lange Wortleitung, Ladungsausgleich, Re-Write...)

- Prefetching **Overfetching**

- Burst

Hoher Energieverbrauch

Kleinere Arrays

Overfetch minimieren

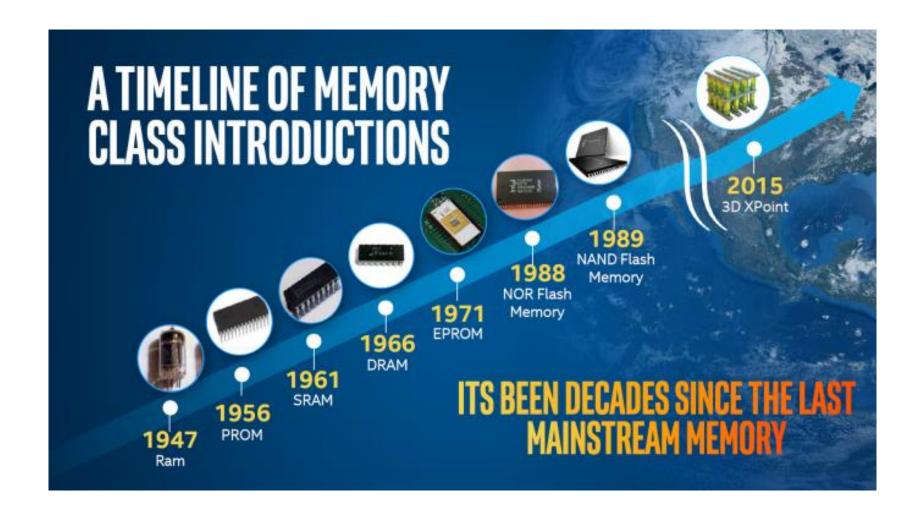

#### "Entwicklung / Potenzial"

- Kapazität verdoppelt sich alle zwei Jahre

- Zugriffszeit verbessert sich nur leicht, eher optimierte Algorithmen / Zugriffsmethoden (Burst, Prefetching, ..), als technische Innovationen

- Bandbreitenlimitationen bei aktueller Bauweisedurch physikalische Gegebenheiten

- Ähnliche, nicht flüchtige Alternativen

### "Synchronous Dynamic Random Access Memory (SDRAM)"

- Synchronisierung der Taktung (durch CPU)

- Vereinfachte Kommunikation einzelner Schnittstellen

- ~ Verdopplung der Geschwindigkeit gegenüber dem Vorgänger

### "Double Data Rate Synchronous Dynamic Random Access Memory (DDR-SDRAM)"

- ~ Doppelte Datenübertragung, da zwei mal pro ,Takt' übertragen wird

- Heutiger Standard, momentan 4. Generation, die 5. ist in Entwicklung

#### "Einsatzgebiete"

Als Hauptspeicher in jeglicher Art von Computer

Desktop Computer

Laptops

**Smartphones**

Drucker

DDR-SDRAM

DIMM (PC Standard) / SO-DIMM (Laptop Standard)

momentan DDR4: bis zu 25 GB/s (single channel), 50 GB/s (dual)

> DDR5: bis zu 50 GB/s (single channel), 100 GB/s (dual)

GDDR-SDRAM (Grafikkarten)

bis zu 576 GB/s momentan GDDR6:

LPDDR-SDRAM (Smartphones)

momentan I PDDR4X: 34 GB/s (64bit)

> LPDDR5: 50 GB/s (64bit)

#### "...Produktion / Markt"

#### Hauptproduzenten

- Samsung

- SK Hynix

- Micron

#### Illegale Preisabsprachen

Nahezu alle großen Produzenten involviert

Preis für DRAM-Elemente hat sich von Juni 2016 bis Januar 2018 (18 Monate) verdreifacht

(zusätzlich cryptocurrency-mining)

#### Umsatzzahlen von Halbleiterspeicherbauelementen im Jahr 2005 (Quelle: Elektronik Scout 2006)

| Speichertechnologie      |                         |              | Umsatz     |

|--------------------------|-------------------------|--------------|------------|

| Flüchtige Speicher (RAM) |                         |              |            |

| Statisches RAM (SRAM)    |                         |              | 2 Mrd. \$  |

| Dynamisches RAM (DRAM)   |                         | 27 Mrd. \$   |            |

| Nichtflüchtige Speicher  |                         |              |            |

| Ausgereiftes Material    | Nur-Lese-Speicher (ROM) |              | 2 Mrd. \$  |

|                          | Flash                   | NAND         | 8 Mrd. \$  |

|                          |                         | NOR          | 9 Mrd. \$  |

| Innovatives Material     |                         | 0,01 Mrd. \$ |            |

| Gesamtumsatz             |                         |              | 48 Mrd. \$ |

Figure 9

2017: etwa 419 Mrd. \$

Datenspeicher

SRAM 00000000

Outro

https://www.youtube.com/watch?v=M-wNC3Z3ZX4

Making Memory Chips – Process Steps

https://www.youtube.com/watch?v=M-wNC3Z3ZX4

Making Memory Chips – Process Steps

- Übersicht

- Aufbau

- Funktionsweise

- Probleme & Lösungen

- Hierarchien / Einsatzgebiete

- Entwicklung / Potenzial

- Produktion / Markt

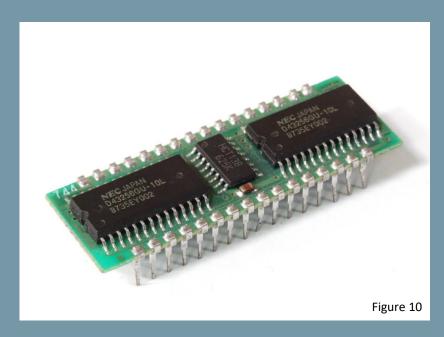

### "Übersicht"

Eine Art von Random-Access Memory, welche jedes Datenbit in einem kleinen integrierten Schaltkreis aus meistens 6 Transistoren speichert.

- Flüchtiger Speicher Transistoren brauchen eine permanent anliegende Betriebsspannung

- Static-RAM Kein Refresh notwendig, jedoch Datenverlust bei Stromausfall

- Sehr schnelle Lese- und Schreibgeschwindigkeit

- Sehr lange Lebensdauer (non-destructive read & write)

- Sehr geringer Energieverbrauch (im standby)

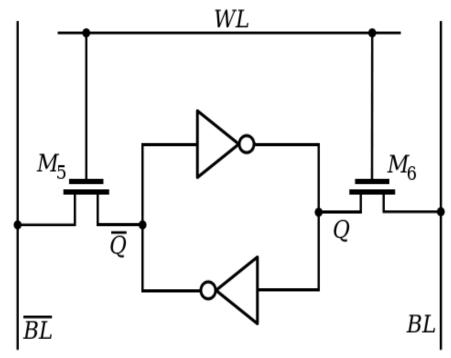

"Aufbau"

- Eine Zelle besteht aus 2

gegeneinander geschalteten

Invertern (jeweils 2 Transistoren),

sowie 2 Schalttransistoren

- = 6 Transistoren (6T-SRAM-Zelle)

Figure 11

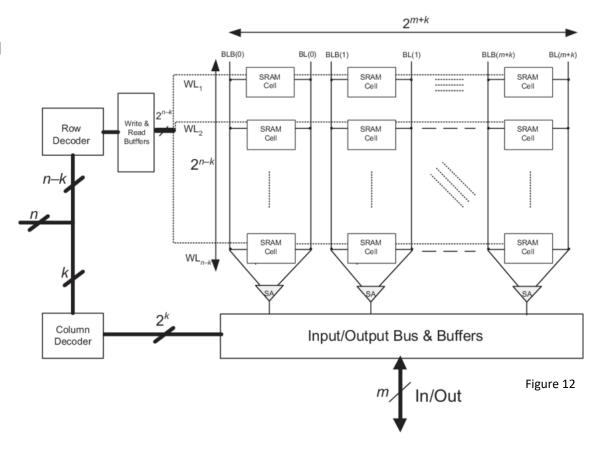

#### "Funktionsweise"

- Fast identischer Aufbau zu DRAM auf höherer Ebene (Unterschied auf Bit-Level)

- Verbindung einer Zelle mit beiden Bitleitungen

- Keine Refresh-Clock, da nicht benötigt

"Probleme & Lösungen"

Variierender Stromverbrauch

- Geringere Taktfrequenz um Verbrauchsobergrenze zu schaffen

- Intelligentes Management um unnötige Zugriffe zu vermeiden

Übertragungsengpässe

Kleinere Module Mehrere Cache-"Level"

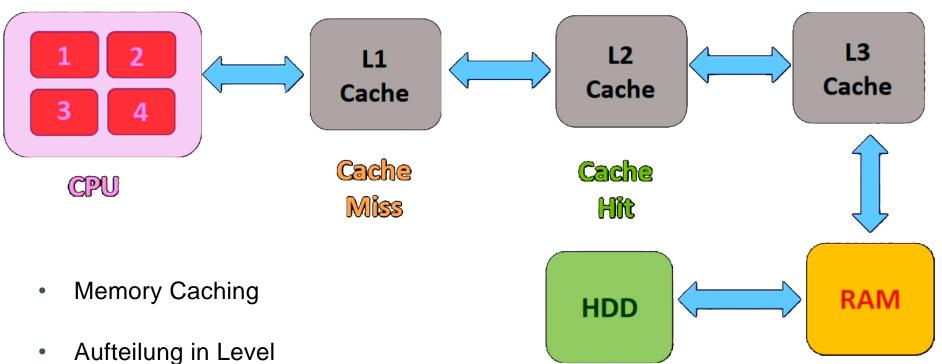

### "Hierarchien / Einsatzgebiet"

- Zugriffshierarchie

Figure 13

### "Hierarchien / Einsatzgebiet"

Figure 14

#### "Entwicklung / Potenzial"

- Schnellster verfügbarer Speicher

- Potenzial "neural networks"

- Kein Endverbraucher-Massenmarkt

#### "Produktion / Markt"

#### Produzenten:

- Micron

- Samsung

- Intel

- Speicher ist größtenteils integriert, kein Endbenutzermarkt

- Eigenproduktion (Intel, ...)

#### Umsatzzahlen von Halbleiterspeicherbauelementen im Jahr 2005 (Quelle: Elektronik Scout 2006)

| Speichertechnologie      |                         |      | Umsatz       |

|--------------------------|-------------------------|------|--------------|

| Flüchtige Speicher (RAM) |                         |      |              |

| Statisches RAM (SRAM)    |                         |      | 2 Mrd. \$    |

| Dynamisches RAM (DRAM)   |                         |      | 27 Mrd. \$   |

| Nichtflüchtige Speicher  |                         |      |              |

| Ausgereiftes Material    | Nur-Lese-Speicher (ROM) |      | 2 Mrd. \$    |

|                          | Flash                   | NAND | 8 Mrd. \$    |

|                          |                         | NOR  | 9 Mrd. \$    |

| Innovatives Material     |                         |      | 0,01 Mrd. \$ |

| Gesamtumsatz             |                         |      | 48 Mrd. \$   |

Figure 9

2017: etwa 419 Mrd. \$

## Übersicht

# DRAM & SRAM

Dynamic random-access memory

Static random-access memory

|                         | SRAM                    | DRAM                                                    | Flash (NAND)    | HDD                                 |

|-------------------------|-------------------------|---------------------------------------------------------|-----------------|-------------------------------------|

| Reciprocal density (F²) | 140                     | 6-8                                                     | 1-4             | 2/3                                 |

| Energy per bit (pJ)     | 0.0005                  | 0.005                                                   | 0.00002         | 5x10 <sup>3</sup> - 10 <sup>4</sup> |

| Read time (ns)          | 0.1-0.3                 | 6                                                       | 100 000         | 5-8x10 <sup>6</sup>                 |

| Write time (ns)         | 0.1-0.3                 | 6                                                       | 100 000         | 5-8x10 <sup>6</sup>                 |

| Retention               | as long as<br>V applied | < <second< td=""><td>years</td><td>years</td></second<> | years           | years                               |

| Endurance<br>(cycles)   | > 10 <sup>16</sup>      | > 10 <sup>16</sup>                                      | 10 <sup>5</sup> | 10 4                                |

Figure 15

|                   | SRAM                                                 | DRAM                                                        |

|-------------------|------------------------------------------------------|-------------------------------------------------------------|

| Kosten            | Relativ teuer                                        | Günstiger als SRAM                                          |

| Performance       | Hohe Geschwindigkeit, niedrige Latenz                | Langsamer, längere<br>Zugriffsdauer                         |

| Speicherdichte    | Gering                                               | Höher, fast wie Flash                                       |

| Speicherkapazität | Gering, KB / MB-Bereich                              | Größer, GB-Bereich                                          |

| Stromverbrauch    | Variierend; Stand-by sehr wenig, bei hoher Last viel | Relativ viel, konstanter Verlust durch Kondensatoren        |

| Speicherart       | Flüchtig, erhalt der Daten<br>solange Strom anliegt  | Flüchtig, regelmäßiger Refresh<br>der Datenzellen notwendig |

| Einsatzgebiet     | CPU-Cache                                            | Arbeitsspeicher                                             |

Simon Alexander Oelgeschläger

# SRAM / DRAM

Eine Präsentation im Modul Proseminar Speicher- und Dateisysteme

#### Bildguellen - Alle Zugriffe im November 2018

- [1] https://www.book-ebooks.com/products/reading-epub/product-id/2998977/title/Non-

- volatile%2BMemories.html?autr=%22Jean-Claude+Lacroix%22

- [2] https://en.wikipedia.org/wiki/Sequential access

- [3] https://de.m.wikipedia.org/wiki/Datei:PS2 RAM Module.jpg

- [4] https://de.wikipedia.org/wiki/Dynamic Random Access Memory

- [5] https://pubweb.eng.utah.edu/~cs7810/pres/11-7810-12.pdf

- [6] INTEGRATED CIRCUIT ENGINEERING CORPORATION DRAM Technology

- [7] https://de.wikipedia.org/wiki/Dynamic Random Access Memory

- [8] https://www.youtube.com/watch?v=Lozf9sceW o

- [9] https://de.wikipedia.org/wiki/Halbleiterspeicher

- [10] http://www.electromyne.de/RAMs---Memory-Other-RAM---Memory-NEC-D43256GU-10L-1Mbit-4x256kbit-SRAM-Static-

- RAM-Memory-Module-DIP-32-Vintage.html

- [11] https://commons.wikimedia.org/wiki/File:SRAM Cell Inverter Loop.png

- [12] https://www.researchgate.net/figure/SRAM-array-structure\_fig4\_276319580

- [13] https://www.youtube.com/watch?v=Zr8WKIOIKsk

- [14] Jawar Singh, Saraju P. Mohanty, Dhiraj K. Pradhan; Robust SRAM Designs and Analysis

- [15] https://www.book-ebooks.com/products/reading-epub/product-id/2998977/title/Non-

- volatile%2BMemories.html?autr=%22Jean-Claude+Lacroix%22

#### Literaturquellen

**Sparsh Mittal**, A Survey of Architectural Techniques for DRAM Power Management

Alex Schönberger, Abschätzung der Leistungssteigerung durch 3D-DRAM und Evaluation einer lokalitätsbasierten Architektur

Integrated Circuit Engineering Coorporation, DRAM TECHNOLOGY

**Fazal Hameed,** DRAM Aware Last-Level-Cache Policies for Multi-core Systems

Michael Linder, Test Set Optimization for Industrial SRAM Testing

Koichiro Ishibashi, Kenichi Osada, Low Power and Reliable SRAM Memory Cell and Array Design

Jawar Singh, Saraju P. Mohanty, Dhiraj K. Pradhan, Robust SRAM Designs and Analysis

#### Informationsquellen

https://www.youtube.com/watch?v=Lozf9sceW o

https://www.youtube.com/watch?v=r787m laR1I faster than DRAM?

https://www.youtube.com/watch?v=4WnTTL 7a1g

EEPROM"

https://www.youtube.com/watch?v=Zr8WKIOIKsk

https://www.youtube.com/watch?v=DLM20pWgMyU

"What is DRAM?"

"SRAM vs DRAM: How SRAM Works? How DRAM Works? Why SRAM is

"Different Types of Memory in Microcontroller: Flash Memory, SRAM and

"Cache Memory Explained"

"Different Types of DRAM: SDRAM/DDR1/DDR2/DDR3/DDR4/LPDDR/GDDR"

https://stackoverflow.com/questions/44564905/what-is-over-fetching-or-under-fetching

https://link.springer.com/book/10.1007%2F978-3-642-19568-6

https://link.springer.com/book/10.1007%2F978-1-4614-0818-5

http://mediatum.ub.tum.de/node?id=1114967

http://tuprints.ulb.tu-darmstadt.de/5551/https://dl.acm.org/citation.cfm?doid=2593069.2593197#

https://publikationen.bibliothek.kit.edu/1000049345https://www.book-ebooks.com/products/reading-epub/product-id/2998977/title/Nonvolatile%2BMemories.html?autr=%22Jean-Claude+Lacroix%22

https://www.anandtech.com/show/9470/intel-and-micron-announce-3d-xpoint-nonvolatile-memory-technology-1000x-higher-performanceendurance-than-nand/5

https://www.sparajuli.com.np/2015/05/difference-between-sram-and-dram.html

http://smithsonianchips.si.edu/ice/cd/MEMORY97/SEC07.PDF

https://www.academia.edu/2475806/A\_survey\_of\_architectural\_techniques\_for\_DRAM\_power\_management

https://www.radio-electronics.com/info/data/semicond/memory/sdram-memory-basics-tutorial.php

http://www.icinsights.com/news/bulletins/Are-The-Major-DRAM-Suppliers-Stunting-DRAM-Demand/

https://github.com/PatternAgents/Electronics One Workshop/wiki/Memory-Circuits

https://pubweb.eng.utah.edu/~cs7810/pres/11-7810-12.pdf

https://www.radio-electronics.com/info/data/semicond/memory/sdram-memory-basics-tutorial.php

https://www.academia.edu/2475806/A survey of architectural techniques for DRAM power management

https://www.engadget.com/2018/07/17/samsungs-new-dram-chip-will-make-phones-run-faster-and-longer/?guccounter=1

https://www.anandtech.com/show/11238/ddr5-to-double-bandwidth-over-ddr4-specification-due-next-year

https://www.anandtech.com/show/13084/samsung-announces-first-lpddr5-64qbps-data-rates

https://www.academia.edu/5010517/A\_Survey\_of\_Architectural\_Techniques\_For\_Improving\_Cache\_Power\_Efficiency

#### Besuchte Informationssammlungen

https://de.wikipedia.org/wiki/Cache

https://de.wikipedia.org/wiki/DDR-SDRAM

https://en.wikipedia.org/wiki/Mobile DDR

https://de.wikipedia.org/wiki/Graphics\_Double\_Data\_Rate

https://de.wikipedia.org/wiki/DDR-SDRAM

https://de.wikipedia.org/wiki/Prefetching

https://de.wikipedia.org/wiki/Integrierter\_Schaltkreis

https://de.wikipedia.org/wiki/Arbeitsspeicher

https://de.wikipedia.org/wiki/Speichermodul

https://de.wikipedia.org/wiki/Halbleiterspeicher

https://en.wikipedia.org/wiki/Random\_access

https://en.wikipedia.org/wiki/Sequential\_access

https://de.wikipedia.org/wiki/Halbleiter

https://en.wikipedia.org/wiki/Volatile\_memory

https://en.wikipedia.org/wiki/DIMM

https://en.wikipedia.org/wiki/Static\_random-access\_memory

https://de.wikipedia.org/wiki/Datenspeicher#Elektronische\_Speicherung\_%E2%80%93\_Halbleiterspeicher

https://de.wikipedia.org/wiki/Synchronous Dynamic Random Access Memory

https://de.wikipedia.org/wiki/Extended\_Data\_Output\_Random\_Access\_Memory

https://de.wikipedia.org/wiki/Synchronous Dynamic Random Access Memory

https://de.wikipedia.org/wiki/Burst-Modus\_(Daten%C3%BCbertragung)

https://de.wikipedia.org/wiki/Metall-Oxid-Halbleiter-Feldeffekttransistor

https://en.wikipedia.org/wiki/Dynamic\_random-access\_memory

|                   | SRAM                                                 | DRAM                                                        |

|-------------------|------------------------------------------------------|-------------------------------------------------------------|

| Kosten            | Relativ teuer                                        | Günstiger als SRAM                                          |

| Performance       | Hohe Geschwindigkeit,<br>niedrige Latenz             | Langsamer, längere<br>Zugriffsdauer                         |

| Speicherdichte    | Gering                                               | Höher, fast wie Flash                                       |

| Speicherkapazität | Gering, KB / MB-Bereich                              | Größer, GB-Bereich                                          |

| Stromverbrauch    | Variierend; Stand-by sehr wenig, bei hoher Last viel | Relativ viel, konstanter Verlust durch Kondensatoren        |

| Speicherart       | Flüchtig, erhalt der Daten solange Strom anliegt     | Flüchtig, regelmäßiger Refresh<br>der Datenzellen notwendig |

| Einsatzgebiet     | CPU-Cache                                            | Arbeitsspeicher                                             |